先端技術チップレット試作・受託

#Chiplet #フリップチップボンダー #大規模回路 #チップ化 #個片化 #微細加工技術 #高密度実装 #フリップチップ #集積技術 #チップレット

チップレット試作・受託サービスについて

フリップチップ実装技術を駆使し、新たな半導体実装技術として注目されるチップレット技術の試作をサポートします。お客様のニーズに合わせた幅広い分野での試作から評価まで一貫した対応が可能となります。チップレット技術を用いることによって、機能密度の向上、そしてコストの削減を実現することができます。次世代の移動通信、高性能演算、自動運転、そしてIoTなど、多くの領域でその技術的支援が期待されており、半導体産業のさらなる成長と発展が見込まれています。

outline

チップレットとは

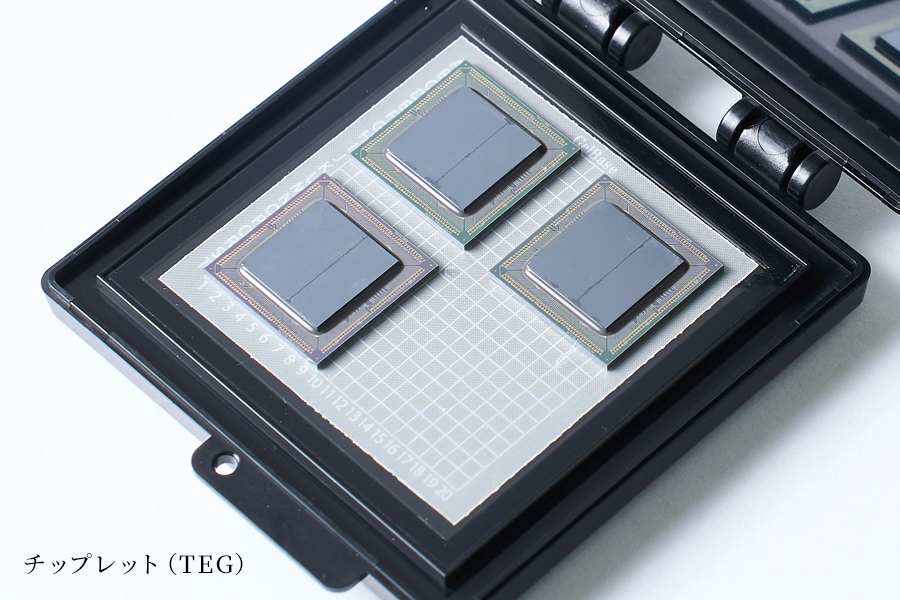

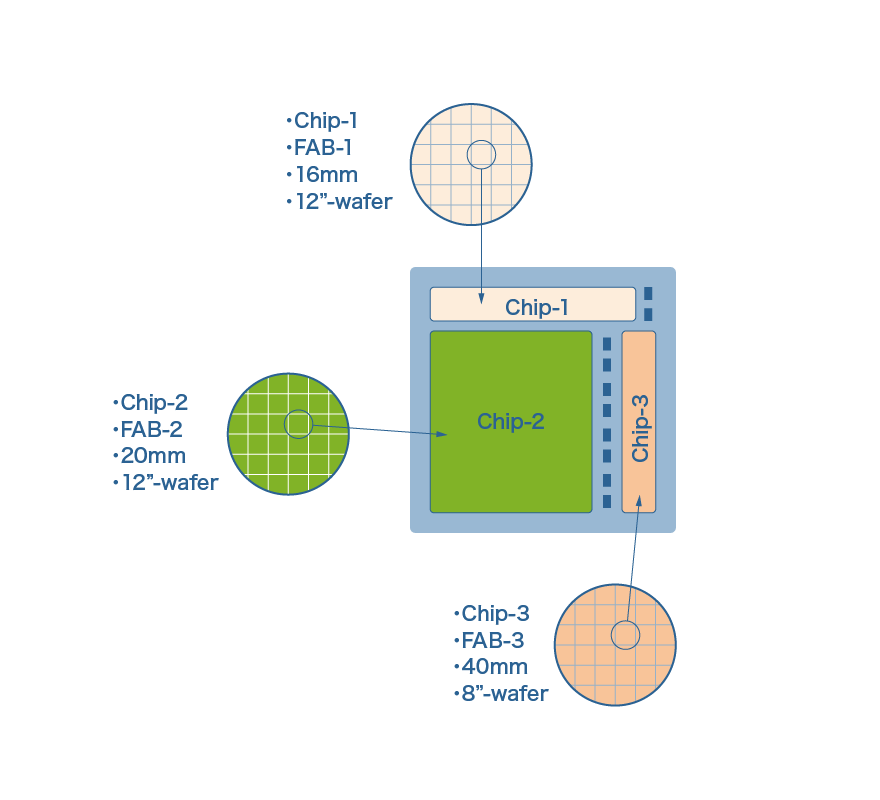

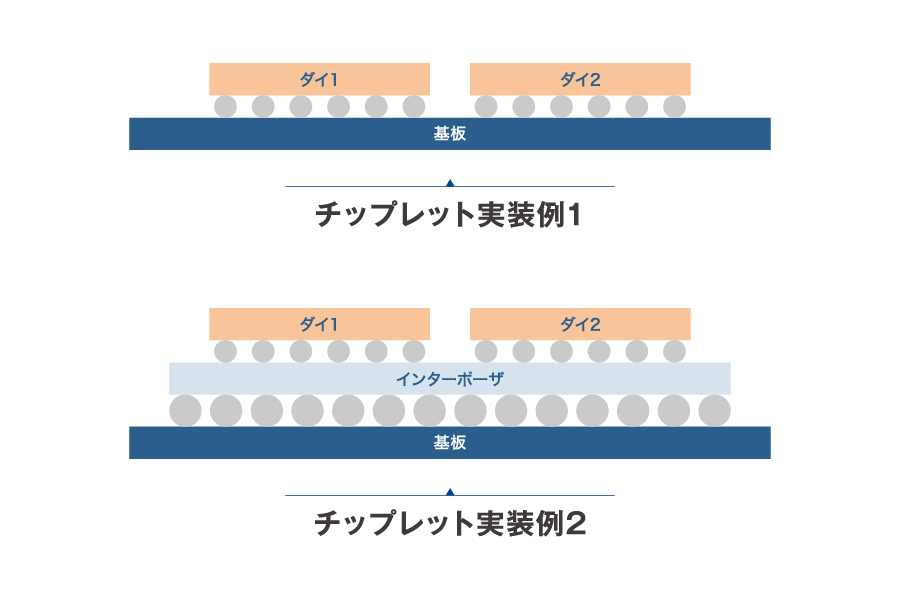

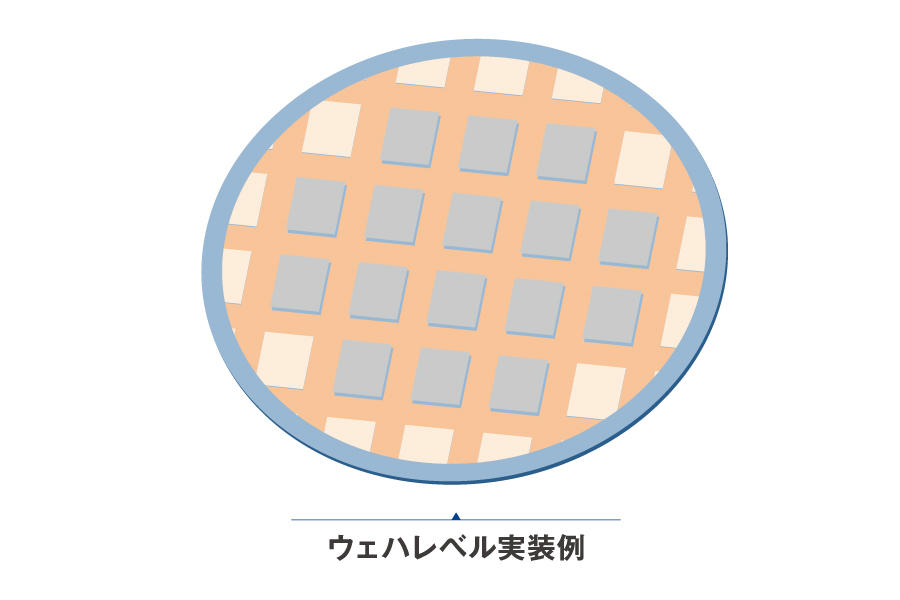

チップレットは、パッケージングアーキテクチャの一部です。インターポーザのような複数な特定機能のダイをdie-to-die相互接続し、パッケージを集積化したものです。チップレットを多用することで、やがてプロセッサ、アナログコンポーネント、メモリなど、チップは機能ごとに複数の小さなチップレットに分割され、一つの新しいチップとして構成します。

装置スペック

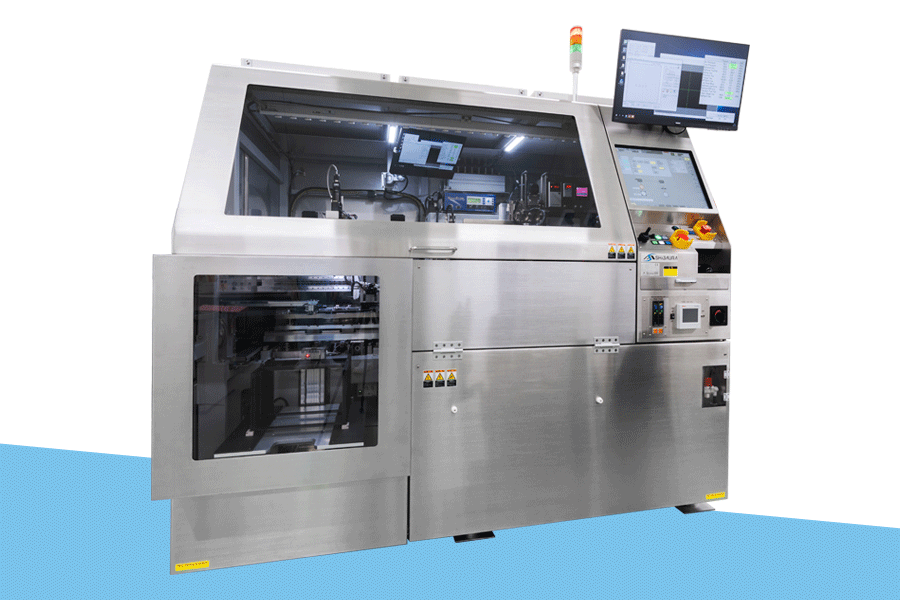

半導体実装の最先端技術と期待されているTSV接合、2.5D・3D実装、FO-WLPなどの実装対応が可能です。搭載ヘッドは低荷重及び高荷重の2ヘッド方式(交換式)とヘッド加熱システムはパルスヒートを採用しておりますので、繊細な実装プロセスも対応可能です。また、チップフェイスアップ高精度実装も対応可能です。

service flow_納品までの流れ

半導体のプロフェショナルにお気軽にご相談をお寄せください。

-

flow01

01_お問い合わせ

-

flow02

02_担当者コンタクト

-

flow03

03_お打ち合わせ

-

flow04

04_仕様決定

-

flow05

05_お見積り提出

-

flow06

06_ご発注

-

flow07

07_作業実施

-

flow08

08_納品